사진. 케이던스

전자 시스템 설계 자동화(EDA) 분야 기업 케이던스 디자인 시스템즈(Cadence Design Systems, 이하 케이던스)가 피지컬 AI, 데이터센터, 고성능 컴퓨팅(이하 HPC)용 칩렛 개발 고객의 설계 복잡도를 낮추고 출시 기간을 단축하기 위해 ‘Chiplet Spec-to-Packaged Parts’ 파트너 에코시스템을 발표했다.

이번 에코시스템에는 Arm, 아터리스(Arteris), 이메모리(eMemory), M31테크놀로지(M31 Technology), 실리콘 크리에이션스(Silicon Creations), 트릴리니어 테크놀로지스(Trilinear Technologies) 등 주요 IP 기업과 실리콘 애널리틱스 전문기업 프로티언텍스(proteanTecs)가 초기 IP 파트너로 참여한다.

케이던스는 삼성전자 파운드리 사업부와 협력해 삼성 파운드리의 SF5A 공정에서 파트너 IP가 사전 통합·검증된 케이던스 피지컬 AI(Cadence Physical AI) 칩렛 플랫폼 기반 실리콘 프로토타입을 구현함으로써 고객의 도입 리스크를 최소화하고 채택을 가속화할 계획이다.

이번 협업으로 케이던스와 삼성 파운드리는 사양 정의 단계부터 실리콘 구현까지 이어지는 엔드투엔드 칩렛 개발 환경을 구축해 고객이 보다 신뢰성 높은 방식으로 첨단 칩렛 설계를 구현하도록 지원한다. 특히 사전 검증된 IP와 공정 최적화 플랫폼을 기반으로 설계 리스크를 낮추고, 차세대 자동차 오토모티브와 피지컬 AI 애플리케이션을 포함한 고성능 시스템 개발을 가속화한다.

삼성전자 파운드리 기술기획 부문 송태중 부사장은 “케이던스와의 협업을 통해 삼성의 SF5A 공정 기술 경쟁력을 실제 실리콘으로 입증할 수 있게 되어 의미가 크다”라며 “이번 협력은 Chiplet Spec-to-Packaged Parts 에코시스템의 성공적인 확장을 이끌고, 고객들이 피지컬 AI를 포함한 차세대 애플리케이션을 위한 신뢰도 높은 첨단 실리콘 솔루션을 보다 빠르게 구현하도록 돕는 중요한 계기가 될 것”이라고 말했다.

케이던스와 Arm은 오랜 기간 축적된 협력 관계를 바탕으로 피지컬 AI와 인프라 AI 전 영역에서 혁신을 가속화하기 위해 협력을 강화하고 있다. 케이던스는 Arm Zena™ 컴퓨트 서브시스템(CSS) 등 핵심 IP를 활용해 피지컬 AI 칩렛 플랫폼과 칩렛 프레임워크를 강화하며, 자동차, 로보틱스, 드론 등 차세대 엣지 AI는 물론 데이터센터, 클라우드, HPC 환경에 필요한 표준 기반 I/O 및 메모리 칩렛 수요까지 충족하는 솔루션을 제공한다.

케이던스 컴퓨트 솔루션 그룹 데이비드 글라스코 부사장은 “케이던스의 새로운 칩렛 에코시스템은 칩렛 활성화 측면에서 중요한 이정표가 된다”라며 “멀티 다이와 칩렛 기반 아키텍처는 성능과 비용 효율성을 동시에 달성하기 위한 핵심 요소로, 케이던스의 사전 통합·검증된 파트너 IP 결합을 통해 고객이 리스크를 최소화한 상태에서 칩렛 도입 목표를 빠르게 실현하도록 지원한다”라고 말했다.

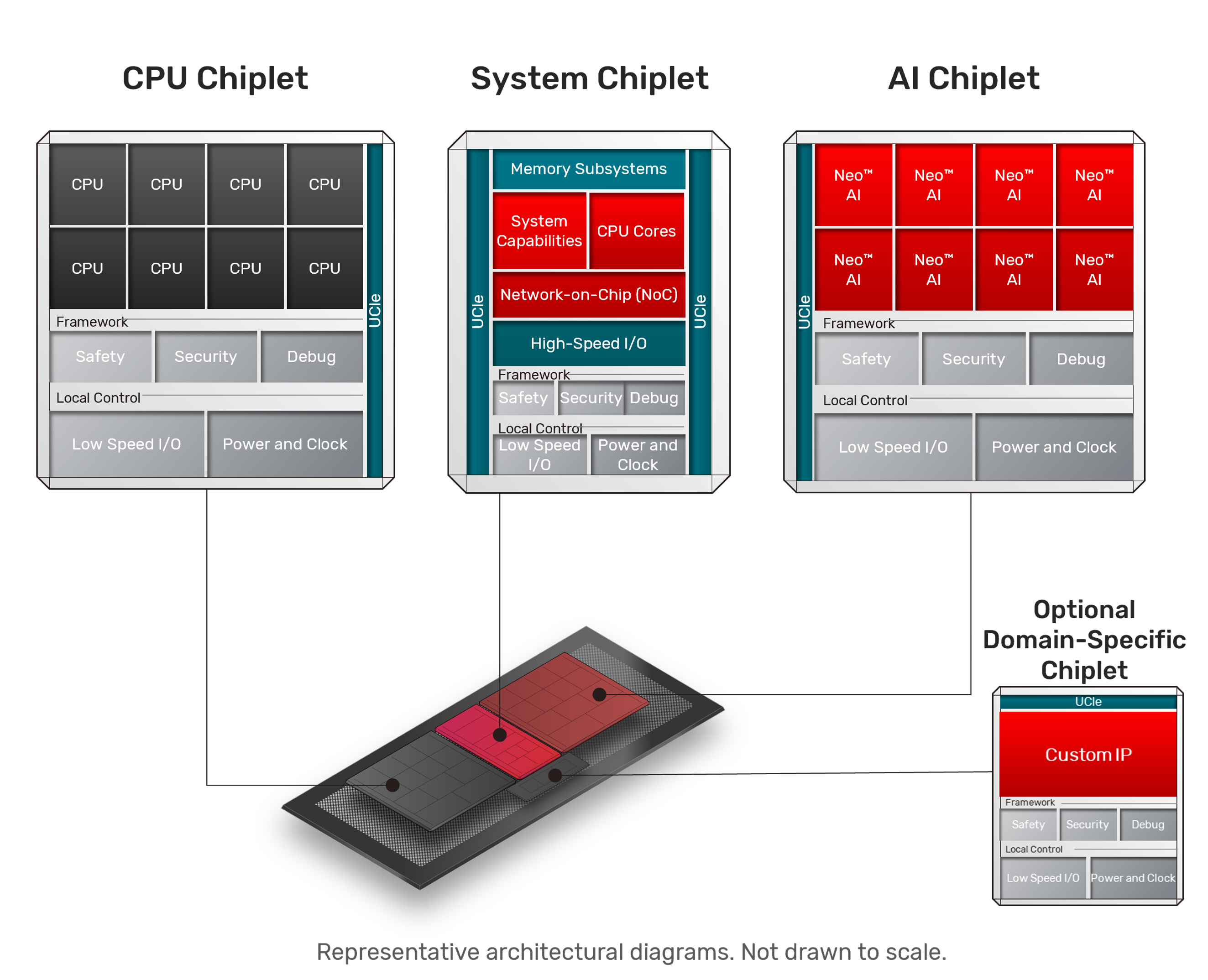

케이던스는 사양 기반 자동화를 통해 케이던스 IP와 파트너 IP를 결합한 칩렛 프레임워크 아키텍처를 생성하며, 칩렛 관리, 보안, 안전 기능과 고급 소프트웨어를 함께 제공한다. 생성된 설계는 Xcelium 로직 시뮬레이터와 Palladium®Z3 엔터프라이즈 에뮬레이션 플랫폼을 활용해 검증되며, 실시간 피드백 기반의 배치·배선 플로우를 지원한다. 해당 아키텍처는 ‘Arm 칩렛 시스템 아키텍처’와 향후 ‘OCP 파운데이셔널 칩렛 시스템 아키텍처’를 포함한 업계 표준을 준수한다.

또한 UCIe(Universal Chiplet Interconnect Express) IP를 통한 다이-투-다이 연결과 함께 LPDDR6·LPDDR5X, DDR5-MRDIMM, PCIe 7.0, HBM4 등 차세대 인터페이스를 빠르게 통합할 수 있는 프로토콜 IP 포트폴리오도 제공한다.