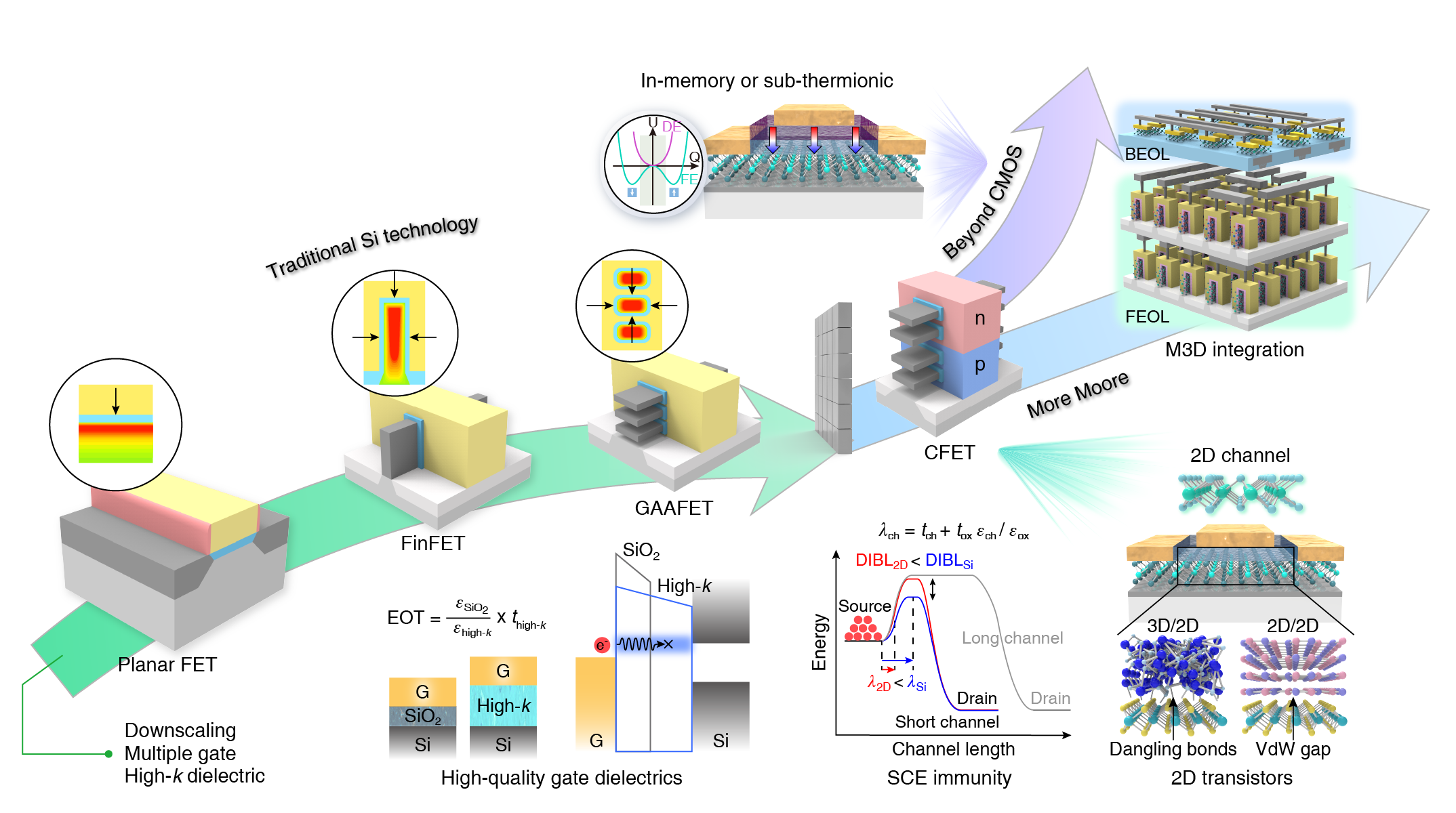

CMOS 로직기술 개발 로드맵 및 옹스트롬급 2D 트랜지스터의 잠재력 / 사진. 서울대학교

서울대학교 공과대학 전기·정보공학부 이철호 교수 연구팀이 2D 트랜지스터의 핵심 기술인 ‘게이트 스택(Gate Stack)’ 발전 방향을 종합적으로 제시하며 차세대 반도체 연구의 중요한 이정표를 세웠다. 이번 성과는 국제 학술지 네이처 일렉트로닉스(Nature Electronics, IF=40.9) 9월 11일(목)에 게재됐다.

게이트 스택은 트랜지스터의 전류를 제어하는 구조로, 전도층 위에 유전체와 금속을 적층해 만든다. 반도체의 성능과 안정성을 좌우하는 핵심 기술로 꼽히지만, 기존 실리콘 기반 공정을 그대로 적용할 경우 유전체 품질 저하, 계면 결함, 전류 누설 등이 발생해 상용화의 걸림돌로 지적됐다.

현재 반도체 산업은 실리콘 CMOS 기술을 기반으로 발전해왔으나, 초미세 공정에 들어서며 한계에 봉착했다. 이에 원자 두께의 얇은 층에서도 전기적 특성이 유지되는 2D 반도체가 차세대 채널 물질로 주목받고 있다. 삼성, TSMC, 인텔, IMEC 등 글로벌 기업과 연구기관들은 이미 2030년대 중반 이후 2D 반도체 트랜지스터를 도입할 계획을 기술 로드맵에 반영하고 대규모 연구개발에 착수한 상태다.

이철호 교수팀은 게이트 스택 형성 방식을 다섯 가지로 분류해 ▲반데르발스(vdW) 계열 유전체 ▲자연 산화 유전체 ▲결정 유전체 전사(quasi-vdW) ▲시드층 기반 고유전막(vdW-seeded) ▲기존 공정 호환(non-vdW-seeded)으로 나눴다. 이어 계면 결함, 산화막 두께, 누설 전류, 임계 전압, 구동 전압 등 성능 지표를 기준으로 평가하고 국제반도체기술로드맵(IRDS) 목표와 비교했다.

또한 강유전체(ferroelectric) 소재를 삽입한 게이트 스택의 가능성을 제시하며 초저전력 로직, 비휘발성 메모리, 인-메모리 컴퓨팅으로 확장할 수 있는 청사진을 제안했다. 특히 BEOL 공정 호환성, 저온 증착(400℃ 이하), 웨이퍼 균일성, 장기 신뢰성 확보 등 실용화 요건까지 구체적으로 제시해 학문적 성과를 넘어 산업적 활용성까지 강조했다.

이철호 교수는 “2D 트랜지스터 상용화의 가장 큰 걸림돌은 고품질 게이트 스택의 구현”이라며 “이번 연구는 이를 극복하기 위한 표준적 청사진을 제시했다는 점에서 학문적·산업적으로 매우 큰 파급력을 지닌다. 앞으로 산학 협력을 통해 실제 소자 집적 및 상용화 연구를 적극적으로 확대해 나갈 계획”이라고 밝혔다.

연구팀은 2D 반도체 게이트 스택 분야에서 국제적으로 주도적 연구를 이어오고 있으며, 실제 소자 제작과 공정 통합까지 포괄하는 성과를 내고 있다. 제1저자인 서울대학교 김연호 박사는 이번 성과를 기반으로 차세대 반도체 집적 소자 분야에서 학문적·산업적 리더십을 발휘할 것으로 기대된다.

이번 연구는 과학기술정보통신부의 차세대 지능형반도체 개발사업과 나노 및 소재기술 개발사업의 지원으로 수행됐으며, 대학원생들은 BK21 Four와 인공지능반도체대학원의 지원을 받았다.